# Power MOSFET 2 Amp, 62 Volts, Logic Level N-Channel DPAK

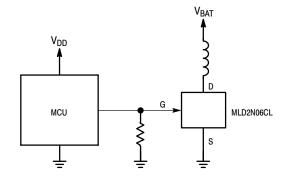

The MLD2N06CL is designed for applications that require a rugged power switching device with short circuit protection that can be directly interfaced to a microcontrol unit (MCU). Ideal applications include automotive fuel injector driver, incandescent lamp driver or other applications where a high in–rush current or a shorted load condition could occur.

This Logic Level Power MOSFET features current limiting for short circuit protection, integrated Gate–Source clamping for ESD protection and integral Gate–Drain clamping for over–voltage protection and technology for low on–resistance. No additional gate series resistance is required when interfacing to the output of a MCU, but a 40  $k\Omega$  gate pulldown resistor is recommended to avoid a floating gate condition.

The internal Gate-Source and Gate-Drain clamps allow the device to be applied without use of external transient suppression components. The Gate-Source clamp protects the MOSFET input from electrostatic voltage stress up to 2.0 kV. The Gate-Drain clamp protects the MOSFET drain from the avalanche stress that occurs with inductive loads. Their unique design provides voltage clamping that is essentially independent of operating temperature.

#### **Features**

• Pb-Free Packages are Available

# MAXIMUM RATINGS (T<sub>J</sub> = 25°C unless otherwise noted)

| Rating                                             | Symbol                            | Value        | Unit |

|----------------------------------------------------|-----------------------------------|--------------|------|

| Drain-to-Source Voltage                            | V <sub>DSS</sub>                  | Clamped      | Vdc  |

| Drain-to-Gate Voltage (R <sub>GS</sub> = 1.0 MΩ)   | $V_{DGR}$                         | Clamped      | Vdc  |

| Gate-to-Source Voltage - Continuous                | V <sub>GS</sub>                   | ±10          | Vdc  |

| Drain Current – Continuous @ T <sub>C</sub> = 25°C | I <sub>D</sub>                    | Self-limited | Adc  |

| Total Power Dissipation @ T <sub>C</sub> = 25°C    | $P_{D}$                           | 40           | W    |

| Electrostatic Voltage                              | ESD                               | 2.0          | kV   |

| Operating & Storage Temperature Range              | T <sub>J</sub> , T <sub>stg</sub> | -50 to 150   | °C   |

#### THERMAL CHARACTERISTICS

| Maximum Junction Temperature                                                                   | T <sub>J(max)</sub>                                                     | 150                 | °C   |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------|------|

| Thermal Resistance, Junction-to-Case Junction-to-Ambient (Note 1) Junction-to-Ambient (Note 2) | $egin{array}{c} R_{	heta JC} \ R_{	heta JA} \ R_{	heta JA} \end{array}$ | 3.12<br>100<br>71.4 | °C/W |

| Maximum Lead Temperature for Soldering Purposes, 1/8" from case for 5 seconds                  | TL                                                                      | 260                 | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- When surface mounted to an FR-4 board using the minimum recommended pad size.

- 2. When surface mounted to an FR-4 board using the 0.5 sq.in. drain pad size.

# ON Semiconductor®

#### www.onsemi.com

| V <sub>(BR)DSS</sub> | R <sub>DS(on)</sub> TYP | I <sub>D</sub> MAX |  |

|----------------------|-------------------------|--------------------|--|

| 62 V (Clamped)       | 400 mΩ                  | 2.0 A              |  |

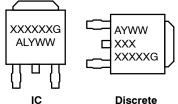

## MARKING DIAGRAM

CASE 369C DPAK STYLE 2

Y = Year

WW = Work Week

L2N06CL = Device Code

G = Pb-Free Package

### **ORDERING INFORMATION**

| Device       | Package           | Shipping <sup>†</sup> |

|--------------|-------------------|-----------------------|

| MLD2N06CL    | DPAK              | 75 Units/Rail         |

| MLD2N06CLG   | DPAK<br>(Pb-Free) | 75 Units/Rail         |

| MLD2N06CLT4  | DPAK              | 2500 Tape & Reel      |

| MLD2N06CLT4G | DPAK<br>(Pb-Free) | 2500 Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

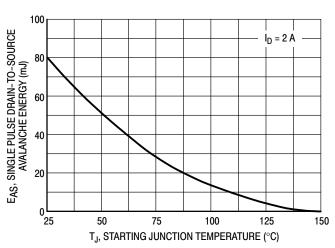

# DRAIN-TO-SOURCE AVALANCHE CHARACTERISTICS

| Rating                                                                                           | Symbol          | Value | Unit |

|--------------------------------------------------------------------------------------------------|-----------------|-------|------|

| Single Pulse Drain-to-Source Avalanche Energy (Starting $T_J = 25$ °C, $I_D = 2.0$ A, L = 40 mH) | E <sub>AS</sub> | 80    | mJ   |

#### **ELECTRICAL CHARACTERISTICS** (T<sub>C</sub> = 25°C unless otherwise noted)

|                                                                                                                                                                                         | Characteristic                                          | Symbol               | Min        | Тур         | Max        | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------|------------|-------------|------------|------|

| OFF CHARACTERISTICS                                                                                                                                                                     | 3                                                       | •                    | •          | •           | •          | •    |

|                                                                                                                                                                                         |                                                         | V <sub>(BR)DSS</sub> | 58<br>58   | 62<br>62    | 66<br>66   | Vdc  |

| Zero Gate Voltage Drain (V <sub>DS</sub> = 40 Vdc, V <sub>GS</sub> = (V <sub>DS</sub> = 40 Vdc, V <sub>GS</sub> =                                                                       | I <sub>DSS</sub>                                        | _<br>_               | 0.6<br>6.0 | 5.0<br>20   | μAdc       |      |

| Gate-Source Leakage Co<br>$(V_G = 5.0 \text{ Vdc}, V_{DS} = (V_G = 5.0 \text{ Vdc}, V_{DS} = 0.0 \text{ Vdc})$                                                                          | I <sub>GSS</sub>                                        | _<br>_               | 0.5<br>1.0 | 5.0<br>20   | μAdc       |      |

| ON CHARACTERISTICS                                                                                                                                                                      | (Note 3)                                                |                      |            |             |            |      |

| Gate Threshold Voltage $ \begin{array}{l} \text{(I}_D = 250 \; \mu Adc,  V_{DS} = V_{GS}) \\ \text{(I}_D = 250 \; \mu Adc,  V_{DS} = V_{GS},  T_J = 150 ^{\circ}\text{C)} \end{array} $ |                                                         |                      | 1.0<br>0.6 | 1.5<br>1.0  | 2.0<br>1.6 | Vdc  |

| Static Drain Current Limit ( $V_{GS} = 5.0 \text{ Vdc}, V_{DS} = (V_{GS} = 5.0 \text{ Vdc}, V_{DS} = 0.0 \text{ Vdc}$                                                                   | I <sub>D(lim)</sub>                                     | 3.8<br>1.6           | 4.4<br>2.4 | 5.2<br>2.9  | Adc        |      |

| Static Drain-to-Source On-Resistance ( $I_D = 1.0 \text{ Adc}, V_{GS} = 5.0 \text{ Vdc}$ ) ( $I_D = 1.0 \text{ Adc}, V_{GS} = 5.0 \text{ Vdc}, T_J = 150^{\circ}\text{C}$ )             |                                                         |                      | -<br>-     | 0.3<br>0.53 | 0.4<br>0.7 | Ω    |

| Forward Transconductan                                                                                                                                                                  | ce (I <sub>D</sub> = 1.0 Adc, V <sub>DS</sub> = 10 Vdc) | 9FS                  | 1.0        | 1.4         | -          | mhos |

| Static Source-to-Drain Diode Voltage (I <sub>S</sub> = 1.0 Adc, V <sub>GS</sub> = 0 Vdc)                                                                                                |                                                         |                      | -          | 1.1         | 1.5        | Vdc  |

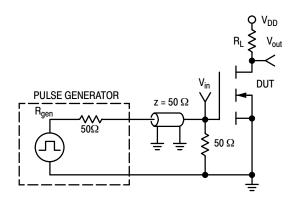

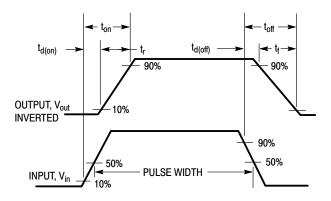

| RESISTIVE SWITCHING                                                                                                                                                                     | CHARACTERISTICS (Note 4)                                |                      |            |             |            |      |

| Turn-On Delay Time                                                                                                                                                                      | urn-On Delay Time                                       |                      |            | 1.0         | 1.5        | μs   |

| Rise Time                                                                                                                                                                               | me (V <sub>DD</sub> = 30 Vdc, I <sub>D</sub> = 1.0 Adc, |                      | -          | 3.0         | 5.0        |      |

| Turn-Off Delay Time                                                                                                                                                                     | V 50.Vdo D 050)                                         |                      |            | 5.0         | 8.0        |      |

| Fall Time                                                                                                                                                                               | t <sub>f</sub>                                          | -                    | 3.0        | 5.0         | 1          |      |

<sup>3.</sup> Pulse Test: Pulse Width ≤ 300 μs, Duty Cycle ≤ 2%.

<sup>4.</sup> Switching characteristics are independent of operating junction temperature.

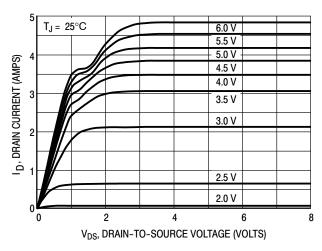

Figure 1. Output Characteristics

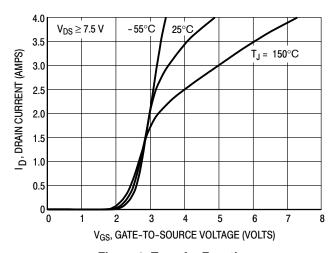

Figure 2. Transfer Function

#### THE POWER MOSFET CONCEPT

From a standard power MOSFET process, several active and passive elements can be obtained that provide on–chip protection to the basic power device. Such elements require only a small increase in silicon area and/or the addition of one masking layer to the process. The resulting device exhibits significant improvements in ruggedness and reliability as well as system cost reduction. The MOSFET device functions can now provide an economical alternative to smart power ICs for power applications requiring low on–resistance, high voltage and high current.

These devices are designed for applications that require a rugged power switching device with short circuit protection that can be directly interfaced to a microcontroller unit (MCU). Ideal applications include automotive fuel injector driver, incandescent lamp driver or other applications where a high in–rush current or a shorted load condition could occur.

## **OPERATION IN THE CURRENT LIMIT MODE**

The amount of time that an unprotected device can withstand the current stress resulting from a shorted load before its maximum junction temperature is exceeded is dependent upon a number of factors that include the amount of heatsinking that is provided, the size or rating of the device, its initial junction temperature, and the supply voltage. Without some form of current limiting, a shorted load can raise a device's junction temperature beyond the maximum rated operating temperature in only a few milliseconds.

Even with no heatsink, the MLD2N06CL can withstand a shorted load powered by an automotive battery (10 to 14 V) for almost a second if its initial operating temperature is under 100°C. For longer periods of operation in the current-limited mode, device heatsinking can extend operation from several seconds to indefinitely depending on the amount of heatsinking provided.

# SHORT CIRCUIT PROTECTION AND THE EFFECT OF TEMPERATURE

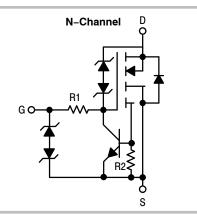

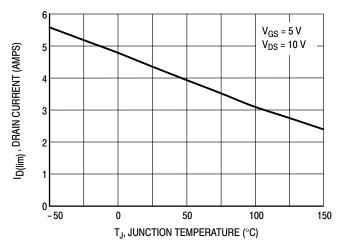

The on-chip circuitry of the MLD2N06CL offers an integrated means of protecting the MOSFET component from high in-rush current or a shorted load. As shown in the schematic diagram, the current limiting feature is provided by an NPN transistor and integral resistors R1 and R2. R2 senses the current through the MOSFET and forward biases the NPN transistor's base as the current increases. As the NPN turns on, it begins to pull gate drive current through R1, dropping the gate drive voltage across it, and thus lowering the voltage across the gate-to-source of the power MOSFET and limiting the current. The current limit is temperature dependent as shown in Figure 3, and decreases from about 2.3 amps at 25°C to about 1.3 A at 150°C.

Since the MLD2N06CL continues to conduct current and dissipate power during a shorted load condition, it is important to provide sufficient heatsinking to limit the device junction temperature to a maximum of 150°C.

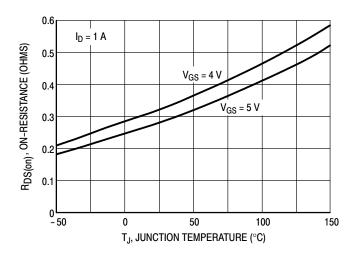

The metal current sense resistor R2 adds about 0.4 ohms to the power MOSFET's on-resistance, but the effect of temperature on the combination is less than on a standard MOSFET due to the lower temperature coefficient of R2. The on-resistance variation with temperature for gate voltages of 4 and 5 V is shown in Figure 5.

Back-to-back polysilicon diodes between gate and source provide ESD protection to greater than 2 kV, HBM. This on-chip protection feature eliminates the need for an external Zener diode for systems with potentially heavy line transients.

Figure 3. I<sub>D(lim)</sub> Variation With Temperature

Figure 4. R<sub>DS(on)</sub> Variation With Gate-To-Source Voltage

Figure 5. On-Resistance Variation With Temperature

Figure 6. Maximum Avalanche Energy versus Junction Temperature

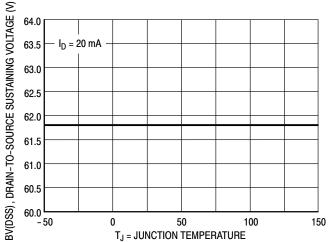

Figure 7. Drain-Source Sustaining Voltage Variation With Temperature

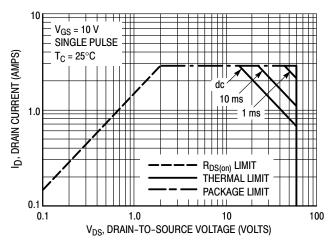

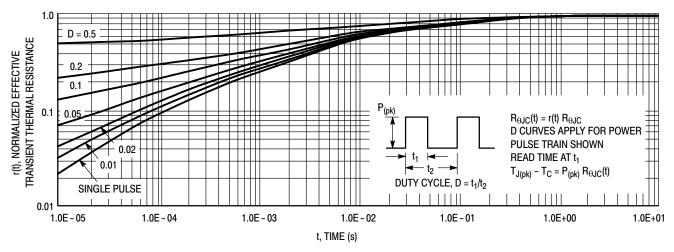

#### FORWARD BIASED SAFE OPERATING AREA

The FBSOA curves define the maximum drain-to-source voltage and drain current that a device can safely handle when it is forward biased, or when it is on, or being turned on. Because these curves include the limitations of simultaneous high voltage and high current, up to the rating of the device, they are especially useful to designers of linear systems. The curves are based on a case temperature of 25°C and a maximum junction temperature of 150°C. Limitations for repetitive pulses at various case temperatures can be determined by using the thermal response curves. ON Semiconductor Application Note, AN569, "Transient Thermal Resistance – General Data and Its Use" provides detailed instructions.

#### **MAXIMUM DC VOLTAGE CONSIDERATIONS**

The maximum drain-to-source voltage that can be continuously applied across the MLD2N06CL when it is in current limit is a function of the power that must be dissipated. This power is determined by the maximum current limit at maximum rated operating temperature

(1.8 A at  $150^{\circ}$ C) and not the  $R_{DS(on)}$ . The maximum voltage can be calculated by the following equation:

$$V_{supply} = \frac{(150 - T_A)}{I_{D(lim)} (R_{\theta JC} + R_{\theta CA})}$$

where the value of  $R_{\theta CA}$  is determined by the heatsink that is being used in the application.

#### **DUTY CYCLE OPERATION**

When operating in the duty cycle mode, the maximum drain voltage can be increased. The maximum operating temperature is related to the duty cycle (DC) by the following equation:

$$T_C = (V_{DS} \times I_D \times DC \times R_{\theta CA}) + T_A$$

The maximum value of  $V_{DS}$  applied when operating in a duty cycle mode can be approximated by:

$$V_{DS} = \frac{150 - T_C}{I_{D(lim)} \times DC \times R_{\theta JC}}$$

Figure 8. Maximum Rated Forward Bias Safe Operating Area (MLD2N06CL)

Figure 9. Thermal Response (MLD2N06CL)

Figure 10. Switching Test Circuit

#### **ACTIVE CLAMPING**

Power MOSFET technology can provide on-chip realization of the popular gate-to-source and gate-to-drain Zener diode clamp elements. Until recently, such features have been implemented only with discrete components which consume board space and add system cost. The power MOSFET technology approach economically melds these features and the power chip with only a slight increase in chip area.

In practice, back-to-back diode elements are formed in a polysilicon region monolithicly integrated with, but electrically isolated from, the main device structure. Each back-to-back diode element provides a temperature compensated voltage element of about 7.2 V. As the polysilicon region is formed on top of silicon dioxide, the diode elements are free from direct interaction with the conduction regions of the power device, thus eliminating parasitic electrical effects while maintaining excellent thermal coupling.

To achieve high gate-to-drain clamp voltages, several voltage elements are strung together; the MLD2N06CL uses 8 such elements. Customarily, two voltage elements are used to provide a 14.4 volt gate-to-source voltage clamp. For the

Figure 11. Switching Waveforms

MLD2N06CL, the integrated gate-to-source voltage elements provide greater than 2.0 kV electrostatic voltage protection.

The avalanche voltage of the gate-to-drain voltage clamp is set less than that of the power MOSFET device. As soon as the drain-to-source voltage exceeds this avalanche voltage, the resulting gate-to-drain Zener current builds a gate voltage across the gate-to-source impedance, turning on the power device which then conducts the current. Since virtually all of the current is carried by the power device, the gate-to-drain voltage clamp element may be small in size. This technique of establishing a temperature compensated drain-to-source sustaining voltage (Figure 7) effectively removes the possibility of drain-to-source avalanche in the power device.

The gate-to-drain voltage clamp technique is particularly useful for snubbing loads where the inductive energy would otherwise avalanche the power device. An improvement in ruggedness of at least four times has been observed when inductive energy is dissipated in the gate-to-drain clamped conduction mode rather than in the more stressful gate-to-source avalanche mode.

# TYPICAL APPLICATIONS: INJECTOR DRIVER, SOLENOIDS, LAMPS, RELAY COILS

The MLD2N06CL has been designed to allow direct interface to the output of a microcontrol unit to control an isolated load. No additional series gate resistance is required, but a 40  $k\Omega$  gate pulldown resistor is recommended to avoid a floating gate condition in the event of an MCU failure. The internal clamps allow the device to be used without any external transistent suppressing components.

В

NOTE 7

|  $\oplus$  | 0.005 (0.13) lacktriangledown C

Ħ

Α1

- h3

Ո

**TOP VIEW**

L3

b2 e

L2 GAUGE

# **DPAK (SINGLE GAUGE)** CASE 369C ISSUE F SCALE 1:1 Α

DETAIL A

C SEATING

C-

SIDE VIEW

**DATE 21 JUL 2015**

#### NOTES:

z

**BOTTOM VIEW**

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: INCHES.

- 3. THERMAL PAD CONTOUR OPTIONAL WITHIN DI-

- MENSIONS b3, L3 and Z.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.006 INCHES PER SIDE.

5. DIMENSIONS D AND E ARE DETERMINED AT THE

- OUTERMOST EXTREMES OF THE PLASTIC BODY.

6. DATUMS A AND B ARE DETERMINED AT DATUM

- 7. OPTIONAL MOLD FEATURE.

|     | INCHES    |       | MILLIM   | ETERS |

|-----|-----------|-------|----------|-------|

| DIM | MIN       | MAX   | MIN      | MAX   |

| Α   | 0.086     | 0.094 | 2.18     | 2.38  |

| A1  | 0.000     | 0.005 | 0.00     | 0.13  |

| b   | 0.025     | 0.035 | 0.63     | 0.89  |

| b2  | 0.028     | 0.045 | 0.72     | 1.14  |

| b3  | 0.180     | 0.215 | 4.57     | 5.46  |

| С   | 0.018     | 0.024 | 0.46     | 0.61  |

| c2  | 0.018     | 0.024 | 0.46     | 0.61  |

| D   | 0.235     | 0.245 | 5.97     | 6.22  |

| E   | 0.250     | 0.265 | 6.35     | 6.73  |

| е   | 0.090 BSC |       | 2.29     | BSC   |

| Н   | 0.370     | 0.410 | 9.40     | 10.41 |

| L   | 0.055     | 0.070 | 1.40     | 1.78  |

| L1  | 0.114     | REF   | 2.90 REF |       |

| L2  | 0.020     | BSC   | 0.51 BSC |       |

| L3  | 0.035     | 0.050 | 0.89     | 1.27  |

| L4  |           | 0.040 |          | 1.01  |

| Z   | 0.155     |       | 3.93     |       |

#### ALTERNATE CONSTRUCTIONS **DETAIL A** ROTATED 90° CW **GENERIC** STYLE 1: STYLE 2: STYLE 3: STYLE 4: STYLE 5: PIN 1. CATHODE 2. ANODE 3. GATE 4. ANODE PIN 1. BASE 2. COLLECTOR 3. EMITTER 4. COLLECTOR PIN 1. ANODE 2. CATHODE 3. ANODE 4. CATHODE PIN 1. GATE 2. ANODE 3. CATHODE 4. ANODE PIN 1. GATE 2. DRAIN

Z

**BOTTOM VIEW**

С

| 3. EMITTE<br>4. COLLE                       | ER .                                            | 3. SOURCE<br>4. DRAIN | 3. AN                                        | ODE<br>THODE | 3. GATE<br>4. ANODE          | 3. | CATHODE<br>ANODE                  |

|---------------------------------------------|-------------------------------------------------|-----------------------|----------------------------------------------|--------------|------------------------------|----|-----------------------------------|

| STYLE 6:<br>PIN 1. MT1<br>2. MT2<br>3. GATE | STYLE 7:<br>PIN 1. GATE<br>2. COLLE<br>3. EMITT | PI                    | 'LE 8:<br>N 1. N/C<br>2. CATHODE<br>3. ANODE |              | ODE<br>THODE<br>SISTOR ADJUS | 2. | 0:<br>CATHODE<br>ANODE<br>CATHODE |

| 4. MT2                                      | <ol><li>COLLE</li></ol>                         | ECTOR                 | <ol><li>CATHODE</li></ol>                    | 4. CA        | THODE                        | 4. | ANODE                             |

# **MARKING DIAGRAM\***

XXXXXX = Device Code = Assembly Location Α L = Wafer Lot Υ = Year WW = Work Week

\*This information is generic. Please refer to device data sheet for actual part marking.

= Pb-Free Package

G

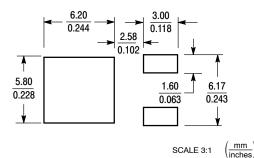

# **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON10527D         | Electronic versions are uncontrolled except when accessed directly from the Document Repo<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | DPAK (SINGLE GAUGE) |                                                                                                                                                                              | PAGE 1 OF 1 |  |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative