घरब्लॉगपूर्ण योजक के लिए विस्तृत गाइड

पूर्ण योजक के लिए विस्तृत गाइड

डिजिटल इलेक्ट्रॉनिक्स और कंप्यूटर इंजीनियरिंग के दायरे में, Adders सबसे आवश्यक बिल्डिंग ब्लॉकों में से एक का प्रतिनिधित्व करते हैं, जो अधिक जटिल अंकगणितीय सर्किट के निर्माण और कार्यक्षमता में महत्वपूर्ण है।अंकगणितीय लॉजिक यूनिट (ALU) के अभिन्न घटकों के रूप में, ADDERS कई कंप्यूटिंग संचालन की सुविधा प्रदान करता है, जो कि सिस्टम संचालन के लिए आवश्यक बुनियादी अंकगणित से लेकर जटिल तार्किक कार्यों तक होता है।उनका डिज़ाइन, जो साधारण आधे-चौंकाने वाले से अधिक जटिल पूर्ण जोड़ों तक भिन्न हो सकता है, डिजिटल सिस्टम के भीतर प्रसंस्करण की दक्षता और गति को बढ़ाने में महत्वपूर्ण भूमिका निभाता है।यह लेख विभिन्न प्रकार के एडर्स की विस्तृत वास्तुकला और कार्यात्मक बारीकियों में, आधुनिक कंप्यूटिंग प्रौद्योगिकी में उनकी महत्वपूर्ण भूमिका को दर्शाता है और डिजिटल लॉजिक डिजाइन के व्यापक संदर्भ के भीतर उनके परिचालन तर्क, सर्किटरी और अनुप्रयोगों की खोज करता है।

सूची

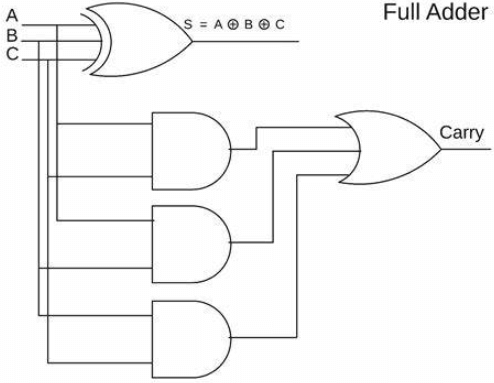

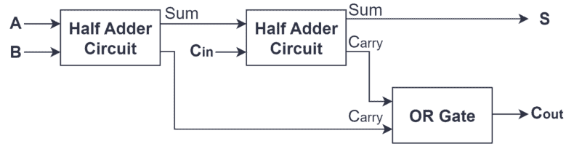

चित्र 1: पूर्ण योजक

एक योजक इलेक्ट्रॉनिक इंजीनियरिंग और डिजिटल लॉजिक डिज़ाइन में एक मौलिक घटक है और अधिक जटिल कंप्यूटर सिस्टम में एक केंद्रीय भूमिका निभाता है।अंकगणित लॉजिक यूनिट (ALU) के एक भाग के रूप में, योजक विभिन्न प्रकार के आवश्यक कंप्यूटिंग कार्यों को संभालता है।पूरे प्रोसेसर की दक्षता और प्रदर्शन सीधे योजक के डिजाइन और कार्यक्षमता से प्रभावित होते हैं।

प्रोसेसर में, योजक का उपयोग न केवल जोड़ और घटाव जैसे बुनियादी अंकगणितीय संचालन के लिए किया जाता है, बल्कि यह तार्किक संचालन की एक विस्तृत श्रृंखला में भी संलग्न होता है।उदाहरण के लिए, प्रोग्राम चलाते समय, प्रोसेसर को अक्सर नए मेमोरी पते की गणना करने की आवश्यकता होती है।यह आमतौर पर वर्तमान पते से जोड़कर या घटाने के द्वारा किया जाता है - योजक द्वारा किया गया एक कार्य।वे लूप पुनरावृत्तियों की संख्या और काउंटरों को बढ़ाने और घटने से समग्र प्रवाह को नियंत्रित करते हैं।अधिक जटिल अनुप्रयोगों में, जैसे कि टेबल इंडेक्सिंग, Adders जल्दी से ऑफसेट की गणना करके डेटा का पता लगाते हैं।यह डेटाबेस प्रबंधन प्रणालियों, संकलक निर्माण और बड़े पैमाने पर डेटा प्रसंस्करण के लिए महत्वपूर्ण है।Adders बहु-स्तरीय कैश सिस्टम में कुछ मैपिंग तकनीकों को लागू करने में भी महत्वपूर्ण हैं, कैश में डेटा की स्थिति को निर्धारित करने के लिए अंकगणितीय संचालन का उपयोग करते हुए, इस प्रकार पहुंच दक्षता का अनुकूलन करते हैं।

तकनीकी रूप से, Adders समानांतर, सीरियल और पाइपलाइन Adders सहित विभिन्न सर्किट डिजाइनों के माध्यम से लागू किए जाते हैं।समानांतर योजक एक साथ कई अंकों को संभालने की उनकी क्षमता के लिए इष्ट हैं, जो उन्हें तेजी से गणना की आवश्यकता वाले परिदृश्यों के लिए उपयुक्त बनाते हैं।दूसरी ओर, सीरियल एडर्स, प्रति घड़ी चक्र में एक बिट की प्रक्रिया करते हैं और संसाधन-सीमित या कम-शक्ति वातावरण के लिए आदर्श होते हैं।पाइपलाइन एडर्स अतिरिक्त प्रक्रिया को कई चरणों में विभाजित करते हैं, प्रत्येक अतिरिक्त ऑपरेशन के एक हिस्से को संभालते हैं।यह डिज़ाइन कम्प्यूटेशन की गति को बढ़ाता है, विशेष रूप से उच्च-प्रदर्शन कंप्यूटिंग वातावरण में।

एक आधा हिस्सा सर्किट डिजिटल इलेक्ट्रॉनिक्स में एक मौलिक बिल्डिंग ब्लॉक है, जिसे विशेष रूप से दो एकल बाइनरी अंकों को जोड़ने के लिए डिज़ाइन किया गया है।यह सर्किट एक पूर्ण योजक की नींव बनाता है और अधिक जटिल तर्क सर्किट डिजाइनों को समझने के लिए महत्वपूर्ण है।एक आधे योजक में, दो प्राथमिक इनपुट होते हैं, जिन्हें ए और बी लेबल किया जाता है, जो क्रमशः ऑगेंड और एडेंड का प्रतिनिधित्व करते हैं।यह सेटअप इसे पिछली गणनाओं से कैरी इनपुट की आवश्यकता के बिना राशि और कैरी आउटपुट की गणना करने में सक्षम बनाता है।

एक आधे-ऊपर के कोर में दो लॉजिक गेट होते हैं: एक XOR गेट और An और गेट।XOR गेट SUM आउटपुट उत्पन्न करने के लिए जिम्मेदार है।यह एक सरल नियम के तहत संचालित होता है जहां यह 1 को आउटपुट करता है यदि इसका केवल एक इनपुट 1 है;अन्यथा, यह एक 0. और गेट आउटपुट करता है, दूसरी ओर, कैरी आउटपुट को संभालता है।यह केवल 1 का उत्पादन करता है जब इसके दोनों इनपुट 1 होते हैं, जो बाइनरी जोड़ की मूलभूत आवश्यकताओं के साथ पूरी तरह से संरेखित होते हैं।

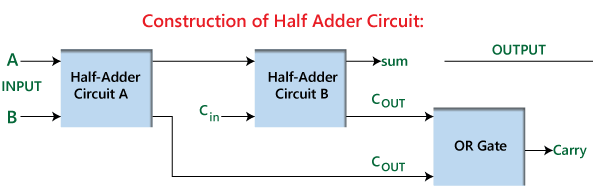

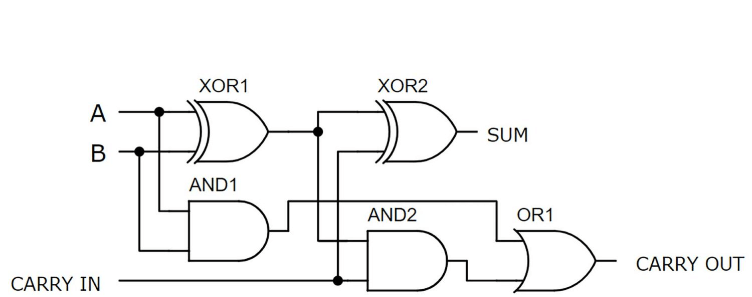

चित्र 2: आधे योजक का निर्माण

यह कुशल और सीधा डिजाइन आधा योजक न केवल स्वतंत्र रूप से बुनियादी बाइनरी जोड़ प्रदर्शन करने की अनुमति देता है, बल्कि एक पूर्ण योजक बनाने के लिए एक बिल्डिंग ब्लॉक के रूप में भी काम करता है।एक पूर्ण योजक का निर्माण एक अतिरिक्त या गेट के साथ दो आधे योजकों को मिलाकर किया जाता है।इस सेटअप में, पहला आधा योजक प्रारंभिक अतिरिक्त कार्य पर ले जाता है, जो एक प्रारंभिक राशि उत्पन्न करता है और कैरी करता है।दूसरी छमाही योजक तब अतिरिक्त कैरी इनपुट के साथ पहले से कैरी को संसाधित करती है।अंत में, या गेट अंतिम कैरी आउटपुट का उत्पादन करने के लिए दो कैरी आउटपुट का विलय करता है।यह व्यवस्था योजक की कार्यक्षमता को बढ़ाती है, जिससे इसे अधिक जटिल मल्टी-बिट अतिरिक्त कार्यों को संभालने में सक्षम बनाया जाता है, जो डिजिटल सर्किट डिजाइन में व्यापक एप्लिकेशन और आधे एडर्स के महत्व को प्रदर्शित करता है।

एक पूर्ण योजक डिजिटल लॉजिक डिज़ाइन में एक उन्नत घटक है, जो तीन सिंगल-बिट बाइनरी इनपुट को संभालने के लिए सुसज्जित है, जिसे आमतौर पर ए, बी और कैरी-इन (CIN) के रूप में लेबल किया जाता है।यह डिज़ाइन पूर्ण योजक को एक एकल ऑपरेशन में पिछले लोअर-ऑर्डर गणना से कैरी को शामिल करके जटिल द्विआधारी परिवर्धन को कुशलता से संसाधित करने की अनुमति देता है।

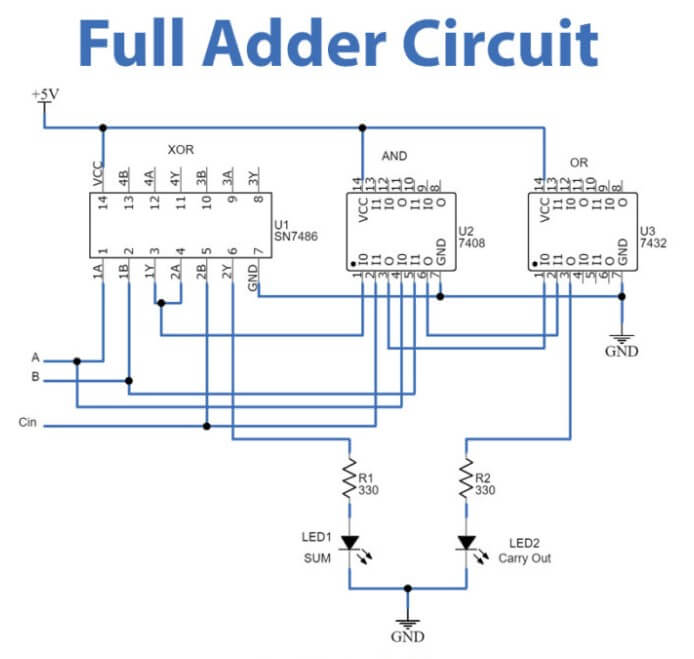

चित्र 3: पूर्ण योजक सर्किट

कार्यात्मक रूप से, एक पूर्ण योजक एक दो अंकों की राशि का उत्पादन कर सकता है, जिसका अर्थ है कि इसका आउटपुट 0 से 3 तक हो सकता है, और यह एक कैरी-आउट (Cout) भी का उत्पादन कर सकता है।ऐसा इसलिए होता है, जब सभी इनपुट बिट्स को 1 (a = 1, b = 1, cin = 1) पर सेट किया जाता है, तो SUM आउटपुट 1 (बाइनरी 01 का प्रतिनिधित्व करते हुए) होगा, और 1 का कैरी-आउट उत्पन्न होता है, यह दर्शाता है किएक अतिरिक्त कैरी को अगले उच्च बिट में पारित करने की आवश्यकता है।

संरचनात्मक रूप से, पूर्ण योजक में आम तौर पर दो आधे योजक और एक या गेट होते हैं।पहला-आधा योजक इनपुट ए और बी लेता है, एक प्रारंभिक राशि और एक कैरी सिग्नल उत्पन्न करता है।इस प्रारंभिक राशि को तब ले जाया जाता है, साथ ही कैरी-इन (CIN), दूसरे हाफ में।दूसरी छमाही योजक की भूमिका इस राशि को पहले हाफ योजर से CIN में जोड़ने के लिए है, एक और राशि और एक नया कैरी आउटपुट का उत्पादन करती है।इसके साथ ही, पहले हाफ योजक से कैरी आउटपुट और दूसरे हाफ योजर से कैरी आउटपुट को एक या गेट के माध्यम से विलय कर दिया जाता है, जो पूर्ण योजक के अंतिम कैरी-आउट (कॉट) में समापन होता है।इस संरचना का डिजाइन यह सुनिश्चित करता है कि पूर्ण योजक प्रभावी रूप से इसके संचालन में वाहक के प्रसार को संभालता है, जिससे यह बहु-बिट बाइनरी परिवर्धन को निष्पादित करने के लिए आदर्श है।इस प्रकार, पूर्ण योजर का डिज़ाइन न केवल डेटा प्रोसेसिंग को गति देता है और दक्षता को बढ़ाता है, बल्कि लॉजिक गेट्स के एक सीधे संयोजन के माध्यम से हार्डवेयर कार्यान्वयन की जटिलता को भी सरल करता है, जिससे यह मल्टी-डिगिट जोड़ और अंकगणित लॉजिक यूनिट (ALU) में एक अपरिहार्य घटक बन जाता है।)।

|

पैरामीटर

|

आधा योजक

|

पूर्ण योजक

|

|

विवरण

|

आधा योजक एक कॉम्बिनेशनल लॉजिक है

सर्किट जो दो 1-बिट अंक जोड़ता है।आधा हिस्सा दोनों का एक योग पैदा करता है

इनपुट।

|

एक पूर्ण योजक एक संयोजन तर्क है

सर्किट जो तीन एक-बिट बाइनरी नंबरों पर एक अतिरिक्त ऑपरेशन करता है।

पूर्ण योजक तीन इनपुट और कैरी वैल्यू का एक योग पैदा करता है।

|

|

पिछला कैरी

|

पिछले कैरी का उपयोग नहीं किया जाता है।

|

पिछले कैरी का उपयोग किया जाता है।

|

|

इनपुट

|

आधे योजर में, दो इनपुट बिट्स होते हैं (ए,

बी)।

|

पूर्ण योजक में, तीन इनपुट बिट्स हैं

(ए, बी, सीमें)।

|

|

आउटपुट

|

उत्पन्न आउटपुट दो बिट्स-राशि का है

और 2 बिट्स के इनपुट से ले जाते हैं।

|

उत्पन्न आउटपुट दो बिट्स-राशि का है

और 3 बिट्स के इनपुट से ले जाते हैं।

|

|

इसके समान इस्तेमाल किया

|

एक आधे-ऊपर सर्किट का उपयोग नहीं किया जा सकता है

उसी तरह एक फुल-एड सर्किट के रूप में।

|

एक पूर्ण योजक सर्किट का उपयोग जगह में किया जा सकता है

एक आधा योजक सर्किट का।

|

|

विशेषता

|

यह सरल और लागू करना आसान है

|

एक पूर्ण योजक का डिजाइन जैसा नहीं है

एक आधे योजक के रूप में सरल।

|

|

तार्किक अभिव्यक्ति

|

आधे योजक के लिए तार्किक अभिव्यक्ति है:

S = a⊕b;C = a*b।

|

पूर्ण योजक के लिए तार्किक अभिव्यक्ति है:

S = a⊕b⊕cin;सीबाहर= (ए*बी)+(सीमें*(A) B))।

|

|

तर्क द्वार

|

इसमें एक पूर्व-या गेट और एक और एक होता है

दरवाज़ा।

|

इसमें दो पूर्व-या, दो और गेट होते हैं,

और एक या गेट।

|

|

अनुप्रयोग

|

इसका उपयोग कैलकुलेटर, कंप्यूटर में किया जाता है,

डिजिटल मापने वाले उपकरण, आदि।

|

इसका उपयोग कई बिट परिवर्धन में किया जाता है,

डिजिटल प्रोसेसर, आदि।

|

|

वैकल्पिक नाम

|

आधे के लिए कोई वैकल्पिक नाम नहीं है

योजक।

|

एक पूर्ण योजक को एक रिपल-कैरी के रूप में भी जाना जाता है

योजक।

|

चार्ट

1: आधे योजक और पूर्ण योजक के बीच अंतर

एक पूर्ण योजक की सत्य तालिका अपने परिचालन तर्क को समझने की कुंजी है, जो बाइनरी इनपुट संयोजनों और उनके संबंधित आउटपुट के बीच सटीक संबंध का विस्तार करती है।यह तालिका सभी संभावित इनपुट परिदृश्यों और उनके परिणामों को प्रदर्शित करती है, जिससे यह डिजिटल लॉजिक सर्किट के डिजाइन और सत्यापन में एक आवश्यक उपकरण बन जाता है।पूर्ण योजक तीन इनपुटों को संसाधित करता है: ए, बी, और एक कैरी-इन (CIN), जिनमें से प्रत्येक या तो 0 या 1 हो सकता है। इसके परिणामस्वरूप इनपुट के आठ संभावित संयोजनों में परिणाम होते हैं।

इन संयोजनों में से प्रत्येक के लिए, पूर्ण योजक से आउटपुट में एक राशि (SUM) और एक कैरी-आउट (Cout) शामिल हैं।योग तीन इनपुट्स- ए, बी, और सिने का मोडुलो -2 जोड़ (एक्सओआर ऑपरेशन) है।कैरी-आउट तब होता है जब कम से कम दो इनपुट बिट्स होते हैं। यह अनुक्रमिक जोड़ संचालन में कैरी-ओवर को संभालने के लिए पूर्ण योजक की क्षमता को दर्शाता है, उच्च-बिट गणना में सटीकता सुनिश्चित करता है।

वर्णन करने के लिए, इनपुट परिदृश्य पर विचार करें जहां सभी इनपुट 0 (a = 0, b = 0, c-in = 0) हैं।आउटपुट योग 0 होगा, और कैरी भी 0 होगा, यह दर्शाता है कि प्रबंधन करने के लिए कोई अतिरिक्त राशि या कैरी नहीं है।यदि केवल एक इनपुट बिट 1 है, जैसे कि ए = 1, बी = 0, सी-इन = 0, आउटपुट राशि 1 के साथ 1 होगी, यह दिखाते हुए कि कैरी को उच्च बिट में स्थानांतरित करने की कोई आवश्यकता नहीं है।जब दो इनपुट बिट्स 1 होते हैं, जैसे कि = 1, बी = 1, सी-इन = 0, आउटपुट योग 0 है (चूंकि 1+1 बाइनरी में 2 के बराबर होता है, और 0 में मॉडुलो -2 परिणाम होता है), लेकिन कैरी-बाहर 1 है, एक कैरी को दर्शाता है जिसे अगले उच्च बिट में पारित करने की आवश्यकता है।सबसे जटिल परिदृश्य तब होता है जब सभी तीन इनपुट बिट्स 1 (ए = 1, बी = 1, सी-इन = 1) होते हैं;आउटपुट राशि 1 है, और 1 का कैरी-आउट है, यह सुझाव देते हुए कि कैरी मैनेजमेंट को भी उच्च बिट्स पर भी आवश्यक हो सकता है।

|

ए

|

बी

|

सीमें

|

एस

|

सीबाहर

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

1

|

चार्ट 2: पूर्ण योजक सत्य तालिका

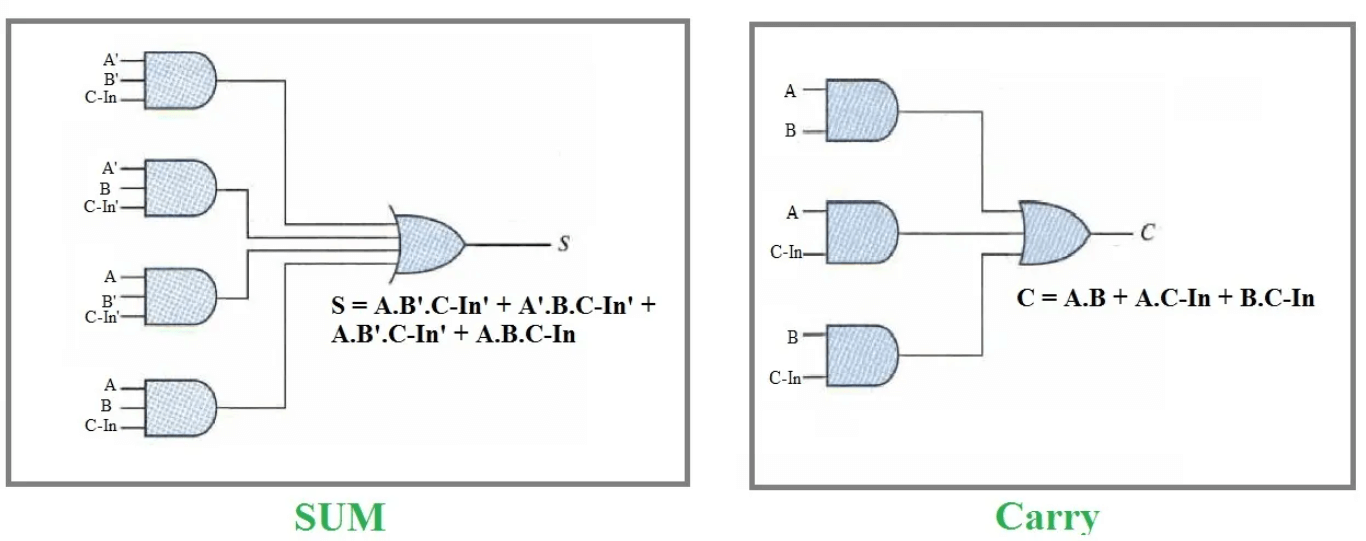

पूर्ण योजक को समझने में सत्य तालिका का उपयोग करके इसकी कार्यक्षमता को विच्छेदित करना शामिल है, जहां इनपुट मूल्यों के अलग-अलग संयोजनों ए, बी, और सी-इन आउटपुट योग और कॉट के लिए नेतृत्व करते हैं।ऑपरेशन को समझने के लिए, हम तर्क समीकरणों को चरण दर चरण को सरल बनाते हैं।

योग के लिए तर्क अभिव्यक्ति

समीकरण अलग -अलग मामलों से शुरू होता है जहां योग 1 के बराबर होता है:

• एक 'बी' CIN + A 'B CIN' + A B 'CIN' + AB CIN

इस समीकरण को CIN के साथ और बिना समूहन द्वारा संघनित किया जा सकता है:

• CIN (A 'B' + AB) + CIN '(A' B + A B ')

यह सरलीकरण एक आसान-से-प्रभाव रूप की ओर जाता है:

• CIN XOR (एक xor b)

इस प्रतिनिधित्व से पता चलता है कि SUM आउटपुट अनिवार्य रूप से A, B, और CIN के बीच XOR ऑपरेशन है, जो बाइनरी जोड़ के मुख्य व्यवहार को कैप्चर करता है, जहां योग एक विषम संख्या के आधार पर टॉगल करता है।

मुट्ठी के लिए तर्क

उन स्थितियों से शुरू करना जहां कैरी उत्पन्न होता है:

• A 'B CIN + A B' CIN + AB C-IN ' + AB CIN

समीकरण को सरल बनाते हुए, हम उन शब्दों की पहचान करते हैं जो आमतौर पर एक कैरी उत्पन्न करते हैं:

• AB + B CIN + A CIN

Cout को लागू करने के लिए एक और विधि की तलाश में, समीकरण को फिर से संगठित किया जा सकता है:

• AB + A CIN + B C-IN (A + A ')

यह उन सभी परिदृश्यों पर कब्जा करने के लिए विस्तार और पुनर्संयोजन करता है जहां कम से कम दो इनपुट 1 हैं:

• AB CIN + AB + A C-IN + A 'B CIN

• AB (1 + CIN) + A C-IN + A 'B CIN

• AB + A C-IN (B + B ') + A' B CIN

• AB + A B 'CIN + A' B CIN

• AB + CIN (A 'B + A B')

Cout के लिए अंतिम कॉम्पैक्ट फॉर्म:

• AB + CIN (एक XOR B)

कैरी-आउट समीकरण का यह संस्करण यह दर्शाता है कि ए और बी दोनों 1 होने पर या तो कैट का उत्पादन कैसे किया जाता है, या जब ए या बी में से एक 1 के साथ 1 होता है, तो इस प्रकार बहु-प्रसार को प्रबंधित करने के लिए आवश्यक तर्क को एनकैप्सुलेट करता है।बिट बाइनरी जोड़।यह सुव्यवस्थित तर्क विशेष रूप से कुशल डिजिटल सर्किट को लागू करने के लिए उपयोगी है।

चित्र 4: एक पूर्ण योजक के समीकरण

एक पूर्ण योजक सर्किट को लागू करने में तीन एकल-बिट बाइनरी इनपुट को कुशलता से संभालने में सक्षम एक उपकरण बनाने के लिए दो आधे योजक और एक या गेट को ध्यान से असेंबल करना शामिल है।यह व्यवस्था सर्किट की जटिलता का अनुकूलन करती है और कुशल और सटीक दोनों गणनाओं को सुनिश्चित करती है।

शुरू करने के लिए, पहला आधा योजक दो प्राथमिक बाइनरी इनपुट, ए और बी लेता है, जो जोड़े जाने वाले मुख्य अंक हैं।इसका मुख्य कार्य इन दो नंबरों के योग और प्रारंभिक कैरी की गणना करना है।यहां, पहला आधा योजक दो परिणाम देता है: एक प्रारंभिक योग (SUM1) और एक प्रारंभिक कैरी (कैरी 1)।SUM1 A और B के XOR ऑपरेशन से लिया गया है, यह दर्शाता है कि कुल में 1 की विषम संख्या है या नहीं।कैरी 1, ए और बी के बीच और संचालन का परिणाम, इंगित करता है कि क्या दोनों अंक 1 हैं, अगले उच्च बिट के लिए एक कैरी की आवश्यकता है।

अगला, दूसरा हाफ योजर प्रक्रिया में शामिल हो गया।यह अपने इनपुट के रूप में SUM आउटपुट SUM1 और तीसरे इनपुट CIN (पिछले गणना से कैरी-इन) का उपयोग करता है।दूसरी छमाही योजक दो आउटपुट का उत्पादन करती है: अंतिम योग परिणाम (SUM2) और माध्यमिक कैरी (कैरी 2)।SUM2, जो SUM1 और CIN का XOR परिणाम है, तीन इनपुट्स के अंतिम योग का प्रतिनिधित्व करता है, जो एकत्रित बाइनरी जोड़ को प्रदर्शित करता है।Carry2, SUM1 और CIN के बीच और संचालन से उभरता हुआ, इन घटकों द्वारा उत्पन्न एक कैरी को इंगित करता है।

चित्र 5: दो आधे योजक का उपयोग करने के साथ पूर्ण योजक सर्किट

अंत में, पूर्ण योजक के डिज़ाइन को पूरा करने के लिए, दोनों आधे एडर्स से कैरी आउटपुट कैरी 1 और कैरी 2 को संभालने के लिए एक या गेट की आवश्यकता होती है।यह या गेट यह सुनिश्चित करता है कि गणना के दौरान उत्पन्न कोई भी कैरी को अंतिम आउटपुट के लिए सही ढंग से अग्रेषित किया जाता है।इसलिए, पूर्ण योजक का अंतिम कैरी आउटपुट (Cout) कैरी 1 और कैरी 2 का परिणाम है।इस या गेट का समावेश यह गारंटी देता है कि सभी संभावित कैरीज़ की सटीक गणना की जाती है और मल्टी-बिट अतिरिक्त संचालन में अगले स्तर तक पहुंची जाती है, जिससे कई बिट्स में अंकगणित संचालन की अखंडता सुनिश्चित होती है।

पूर्ण योजक डिजिटल लॉजिक डिज़ाइन में एक अपरिहार्य भूमिका निभाते हैं, कई लाभ प्रदान करते हैं जो उन्हें विभिन्न कंप्यूटिंग और डेटा प्रोसेसिंग परिदृश्यों में आवश्यक बनाते हैं।उनके प्राथमिक लाभों में उल्लेखनीय लचीलापन, स्विफ्ट प्रसंस्करण गति और कुशल कैरी प्रबंधन शामिल हैं।ये लक्षण जटिल अंकगणितीय संचालन और तर्क कार्यों को निष्पादित करने के लिए पूर्ण योजक को आदर्श बनाते हैं, विशेष रूप से अनुक्रमिक मल्टी-बिट जोड़ की आवश्यकता वाले अनुप्रयोगों में।

लाभ

लचीलापन: एक साथ कई बाइनरी इनपुट (ए, बी, और सिने) को संसाधित करने की उनकी क्षमता में पूर्ण एडर्स एक्सेल।लंबे समय तक बाइनरी नंबरों को संभालने के लिए उन्हें बड़े योजक सरणियों में भी विस्तारित किया जा सकता है।यह स्केलेबिलिटी उच्च-प्रदर्शन अंकगणितीय लॉजिक यूनिट्स (एलस) के निर्माण के लिए महत्वपूर्ण है, जिसे जटिल मल्टी-बिट अंकगणित और तर्क संचालन करना चाहिए।

स्पीड: उनके आंतरिक समानांतर प्रसंस्करण वास्तुकला के लिए धन्यवाद, फुल एडर्स एक घड़ी चक्र में सभी इनपुट के अलावा को पूरा कर सकते हैं, जबकि आउटपुट ले जाने का भी निर्धारण करते हैं।यह क्षमता निरंतर अतिरिक्त संचालन का समर्थन करती है और आधुनिक माइक्रोप्रोसेसरों और उच्च गति कंप्यूटिंग उपकरणों में वास्तविक समय के डेटा प्रसंस्करण के लिए अपरिहार्य है।

नुकसान

हालांकि, पूर्ण योजक भी उल्लेखनीय नुकसान प्रस्तुत करते हैं:

डिजाइन और कार्यान्वयन में जटिलता: पूर्ण योजकों में कई तर्क गेट्स और बहु-स्तरीय कैरी प्रसार शामिल हैं, जो उनके डिजाइन को जटिल बनाते हैं।यह जटिलता न केवल विनिर्माण लागत को बढ़ाती है, बल्कि सर्किट की विश्वसनीयता को भी प्रभावित कर सकती है।

प्रसार देरी के मुद्दे: कैरी प्रचार कई तर्क गेटों से गुजर सकते हैं, प्रत्येक इसकी देरी को जोड़ते हैं।यह बड़े पैमाने पर संचालन के दौरान समग्र कम्प्यूटेशनल गति को सीमित कर सकता है, विशेष रूप से व्यापक कंप्यूटर सिस्टम में और बहुत बड़े पैमाने पर एकीकरण (वीएलएसआई) और उच्च गति वाले प्रोसेसर के डिजाइन में।देरी प्रदर्शन में एक महत्वपूर्ण अड़चन बन सकती है।

इन मुद्दों को कम करने के लिए, इंजीनियर लगातार अधिक कुशल सर्किट डिजाइनों का पता लगाते हैं।रणनीतियों में तेजी से लॉजिक गेट प्रौद्योगिकियों का उपयोग करना, पथ की लंबाई को कम करने के लिए सर्किट लेआउट का अनुकूलन करना, और कैरी प्रसार में देरी को कम करने के लिए कैरी-सेव एडर्स जैसी उन्नत प्रौद्योगिकियों को विकसित करना शामिल है।

पूर्ण योजकों को बड़े पैमाने पर डिजिटल लॉजिक में उपयोग किया जाता है, उनके लचीलेपन और दक्षता के लिए बेशकीमती है, जिससे उन्हें कंप्यूटिंग और डेटा प्रोसेसिंग कार्यों की भीड़ के लिए केंद्रीय बनाया जाता है।उनका आवेदन बुनियादी अंकगणितीय संचालन से जटिल सिग्नल प्रोसेसिंग और सिस्टम नियंत्रण तक फैला है।यहां कुछ प्रमुख क्षेत्रों पर एक विस्तृत नज़र है जहां पूर्ण जोड़ने वाले अभिन्न हैं।

अंकगणितीय सर्किट

पूर्ण जोड़ों के सबसे सीधे उपयोगों में से एक अंकगणितीय सर्किट में है जहां वे बाइनरी जोड़ करते हैं।विशेष रूप से मल्टी-बिट संख्या के अलावा महत्वपूर्ण, पूर्ण एडर्स कैस्केडिंग के माध्यम से लंबे समय तक द्विआधारी अनुक्रमों का प्रबंधन करते हैं।इस व्यवस्था में, प्रत्येक पूर्ण योजक अपनी बिट स्थिति और निचले बिट से कैरी के लिए जोड़ को संभालता है, फिर नए कैरी को अगले उच्च बिट के पूर्ण योजक को पास करता है।यह कैस्केड अंकों की पूरी श्रृंखला में व्यापक बहु-बिट जोड़ को सक्षम करता है।

डाटा प्रासेसिंग

पूर्ण योजक भी उन्नत डेटा प्रोसेसिंग कार्यों जैसे कि डिजिटल सिग्नल प्रोसेसिंग (डीएसपी) को फ़िल्टरिंग और फूरियर ट्रांसफॉर्म के लिए एक महत्वपूर्ण भूमिका निभाते हैं, जहां सटीक और तेजी से अंकगणित संचालन की आवश्यकता होती है।इसके अतिरिक्त, सूचना सुरक्षा के दायरे में, डेटा एन्क्रिप्शन और त्रुटि का पता लगाने और सुधार एल्गोरिदम जैसे समता चेक और चक्रीय अतिरेक चेक (सीआरसी) कोड जनरेशन शामिल हैं, आवश्यक बिट संचालन को निष्पादित करने के लिए पूर्ण योजक महत्वपूर्ण हैं।

काउंटर

डिजिटल काउंटरों में, पूर्ण योजक, विशेष रूप से मॉड्यूलर और सिंक्रोनस काउंटरों में वृद्धि और घटाव कार्यों दोनों को लागू करने के लिए अपरिहार्य हैं।वे सटीक गिनती सुनिश्चित करने के लिए सटीक रूप से कैरी और उधार का प्रबंधन करते हैं।

मल्टीप्लेक्सर्स (MUX) और डेमुलिप्लेक्सर्स (डेमक्स)

मल्टीप्लेक्सर्स और डेमुलप्लेक्सर्स में, फुल एडर्स चैनल चयन और डेटा वितरण में महत्वपूर्ण भूमिका निभाते हैं।वे तर्क में भाग लेते हैं जो निर्धारित करता है कि डेटा इनपुट और आउटपुट के लिए कौन से चैनल का उपयोग किया जाता है, जो तर्क नियंत्रण संकेतों के आधार पर निर्णय लेता है।

स्मृति प्रौद्योगिकी

मेमोरी एड्रेसिंग में, फुल एडर्स डायनामिक रूप से मेमोरी स्थानों तक पहुंचने के लिए पते के संकेतों को उत्पन्न करने में मदद करते हैं।यह डायनेमिक रैंडम-एक्सेस मेमोरी (DRAM) और अन्य स्टोरेज सिस्टम में विशेष रूप से महत्वपूर्ण है, जहां पूर्ण Adders मेमोरी एक्सेस की दक्षता को बढ़ाने के लिए जटिल पते की गणना का समर्थन करते हैं।

अंकगणितीय तर्क इकाइयाँ (ALU)

अंत में, माइक्रोप्रोसेसर्स और डिजिटल सिग्नल प्रोसेसर में अंकगणितीय लॉजिक इकाइयों के मौलिक घटकों के रूप में, पूर्ण योजक महत्वपूर्ण हैं।ALU सभी अंकगणित और तर्क संचालन को संभालता है, पूर्ण Adders सुनिश्चित करने के साथ डेटा को तेजी से और सटीक रूप से दोनों संसाधित किया जाता है।

विभिन्न लॉजिक गेट्स और कॉन्फ़िगरेशन का उपयोग करके पूर्ण एडर्स का निर्माण किया जा सकता है।यहां, हम चार अलग -अलग कार्यान्वयन का पता लगाते हैं, जो उनके सेटअप और परिचालन बारीकियों को उजागर करते हैं।

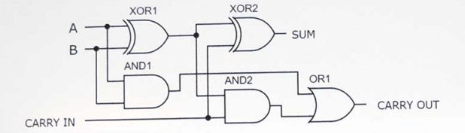

XOR, और, और गेट्स के साथ निर्मित पूर्ण योजक

चित्र 6: XOR, और, और या तर्क गेट्स के साथ निर्मित पूर्ण योजक

यह उदाहरण असतत ट्रांजिस्टर का उपयोग करके एक ब्रेडबोर्ड पर निर्मित एक पूर्ण योजक को दिखाता है।कॉन्फ़िगरेशन में पांच लॉजिक गेट शामिल हैं: दो XOR गेट्स, दो और गेट्स, और एक या गेट, जिसमें कुल 21 ट्रांजिस्टर की आवश्यकता होती है।इनपुट ए और बी ब्रेडबोर्ड के शीर्ष बाएं से जुड़े हैं, जो +5 वी आपूर्ति प्राप्त करते हैं।इन इनपुटों को दो टॉगल स्विच का उपयोग करके नियंत्रित किया जाता है।शीर्ष बाईं ओर दो एल ई डी इनपुट ए और बी की अवस्थाओं को इंगित करते हैं, जबकि दाईं ओर दो एलईडी आउटपुट प्रदर्शित करते हैं।सर्किट में उपयोग किए जाने वाले प्रतिरोध सभी 2.2k ओम हैं।जब इनपुट ए और बी चालू होते हैं और कैरी-इन बंद हो जाता है, तो आउटपुट 10 का द्विआधारी मान दिखाता है, जो कि 2 (1 + 1 + 0 = 10) का प्रतिनिधित्व करता है।पहले 12 ट्रांजिस्टर के साथ बनाया गया XOR गेट्स, प्राथमिक योग को संभालते हैं, जबकि ब्रेडबोर्ड के निचले आधे हिस्से में संचालन के लिए और या गेट होते हैं, रंग-कोडित वायरिंग स्पष्टता और समस्या निवारण को बढ़ाता है।

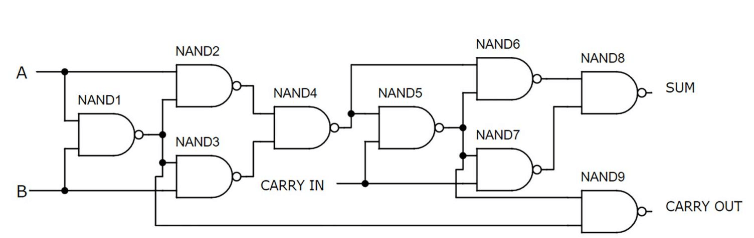

नंद गेट्स का उपयोग करके पूर्ण योजक

चित्र 7: नंद गेट्स का उपयोग करके पूर्ण योजक

यह पूर्ण योजक नौ नंद फाटकों का उपयोग करता है, जिसमें प्रत्येक गेट दो ट्रांजिस्टर से बने होते हैं, कुल 18 ट्रांजिस्टर।यह विधि असतत घटकों का उपयोग करके एक पूर्ण योजक के निर्माण के लिए सबसे सरल और सबसे कुशल तरीकों में से एक है।सभी फाटकों को ब्रेडबोर्ड के ऊपरी आधे हिस्से पर इकट्ठा किया जाता है, जबकि स्विच निचले आधे हिस्से पर कब्जा कर लेते हैं।सर्किट की कार्यक्षमता को इनपुट ए और बी पर और कैरी-इन के साथ प्रदर्शित किया जाता है, जिसके परिणामस्वरूप 10 का आउटपुट बाइनरी मान होता है, जो दशमलव 2 के बराबर होता है।

नोर गेट्स के साथ पूर्ण योजक

चित्र 8: नोर गेट्स के साथ पूर्ण योजक

नौ और न ही गेट्स के साथ निर्मित, प्रत्येक को दो ट्रांजिस्टर की आवश्यकता होती है, यह सेटअप कुल 18 ट्रांजिस्टर का उपयोग करता है।नोर गेट्स के साथ एक पूर्ण योजक का निर्माण एक अच्छा विकल्प प्रदान करता है, लेकिन इसमें नंद गेट्स की तुलना में अधिक जटिल वायरिंग शामिल है।नोर गेट्स में प्रत्येक ट्रांजिस्टर को ग्राउंड किया जाता है, जिसमें कलेक्टरों ने ऑरेंज जम्पर तारों से जुड़ा हुआ है ताकि स्वच्छ और संगठित वायरिंग सुनिश्चित किया जा सके।इस कॉन्फ़िगरेशन को इनपुट ए और बी सक्रिय और कैरी-इन डिएक्टिवेट के साथ दिखाया गया है, जो आउटपुट के लिए अग्रणी है जहां कैरी सक्रिय है और योग बंद है।

एडडर तकनीक के इस अन्वेषण के दौरान, बेसिक हाफ एडर्स से लेकर परिष्कृत पूर्ण योजक डिजाइनों तक, यह स्पष्ट है कि ये घटक डिजिटल इलेक्ट्रॉनिक्स की उन्नति के लिए मूलभूत हैं।परिचालन विशेषताओं और कार्यान्वयन उदाहरणों ने विभिन्न कम्प्यूटेशनल सेटिंग्स में Adders की बहुमुखी प्रतिभा और दक्षता को रेखांकित किया।Adders की संरचना और कार्य की जांच करके, विशेष रूप से उनके सत्य तालिकाओं और विशेषता समीकरणों के माध्यम से, हम उनकी क्षमताओं और बाधाओं में मूल्यवान अंतर्दृष्टि प्राप्त करते हैं।यह ज्ञान अधिक कुशल और तेज कंप्यूटिंग सिस्टम के डिजाइन को आगे बढ़ाने में महत्वपूर्ण है।अंततः, Adders न केवल जटिल द्विआधारी गणना को सरल बनाते हैं, बल्कि डेटा प्रोसेसिंग, मेमोरी आवंटन और डिजिटल सिग्नल प्रोसेसिंग के रूप में विविध क्षेत्रों में प्रौद्योगिकी के प्रसार को भी सक्षम करते हैं।जैसा कि डिजिटल तकनीक विकसित होती है, योजक डिजाइन में चल रहे शोधन और नवाचार अधिक उन्नत कम्प्यूटेशनल आर्किटेक्चर के विकास में एक आधारशिला बनी रहेगी, यह सुनिश्चित करते हुए कि ये मूलभूत घटक डिजिटल सिस्टम डिजाइन और कार्यान्वयन के दिल में बने हुए हैं।

अक्सर पूछे जाने वाले प्रश्न [FAQ]

1. एक पूर्ण योजक सर्किट क्या है?

एक पूर्ण योजक एक डिजिटल सर्किट है जो एक राशि और एक कैरी आउटपुट का उत्पादन करने के लिए तीन बाइनरी बिट्स जोड़ता है।यह तीन इनपुटों के अलावा को संभालने के लिए डिज़ाइन किया गया है: दो महत्वपूर्ण बिट्स और एक कैरी-इन बिट पिछले जोड़ से।यह इसे बहु-बिट बाइनरी नंबरों को जोड़ने के लिए क्रमिक चरणों में उपयोग करने की अनुमति देता है।

2. पूर्ण योजक में कितने और, या, xor?

एक विशिष्ट पूर्ण योजक में शामिल हैं:

योग उत्पन्न करने के लिए दो XOR गेट।

कैरी-आउट गणना में योगदान करने के लिए दो और द्वार।

कैरी-आउट आउटपुट को अंतिम रूप देने के लिए एक या गेट।

3. पूर्ण योजक में कैरी इनपुट क्या है?

एक पूर्ण योजक में कैरी इनपुट (CIN) मल्टी-बिट बाइनरी जोड़ में पिछले निचले महत्वपूर्ण बिट्स के अलावा से बिट है।यह पूर्ण योजक को वर्तमान राशि और नए कैरी-आउट की गणना करते समय इस पिछले कैरी पर विचार करने की अनुमति देता है।

4. एक आधे योजक के बजाय एक पूर्ण योजक का उपयोग क्यों करें?

एक पूर्ण योजक का उपयोग एक आधा योजक के बजाय किया जाता है क्योंकि यह तीन बिट्स (पिछले परिवर्धन से कैरी सहित) को जोड़ सकता है, जिससे मल्टी-बिट संख्या जोड़ने के लिए एक साथ पीछा करने के लिए उपयुक्त हो जाता है।एक आधा हिस्सा केवल दो बिट्स जोड़ सकता है और एक कैरी-इन के लिए एक प्रावधान नहीं है, जो अनुक्रमिक कैरी प्रसार के बिना बाइनरी जोड़ के सबसे सरल रूपों तक इसके उपयोग को सीमित करता है।